打开 Cirona,在右边对话框里输入一行 SPEC。

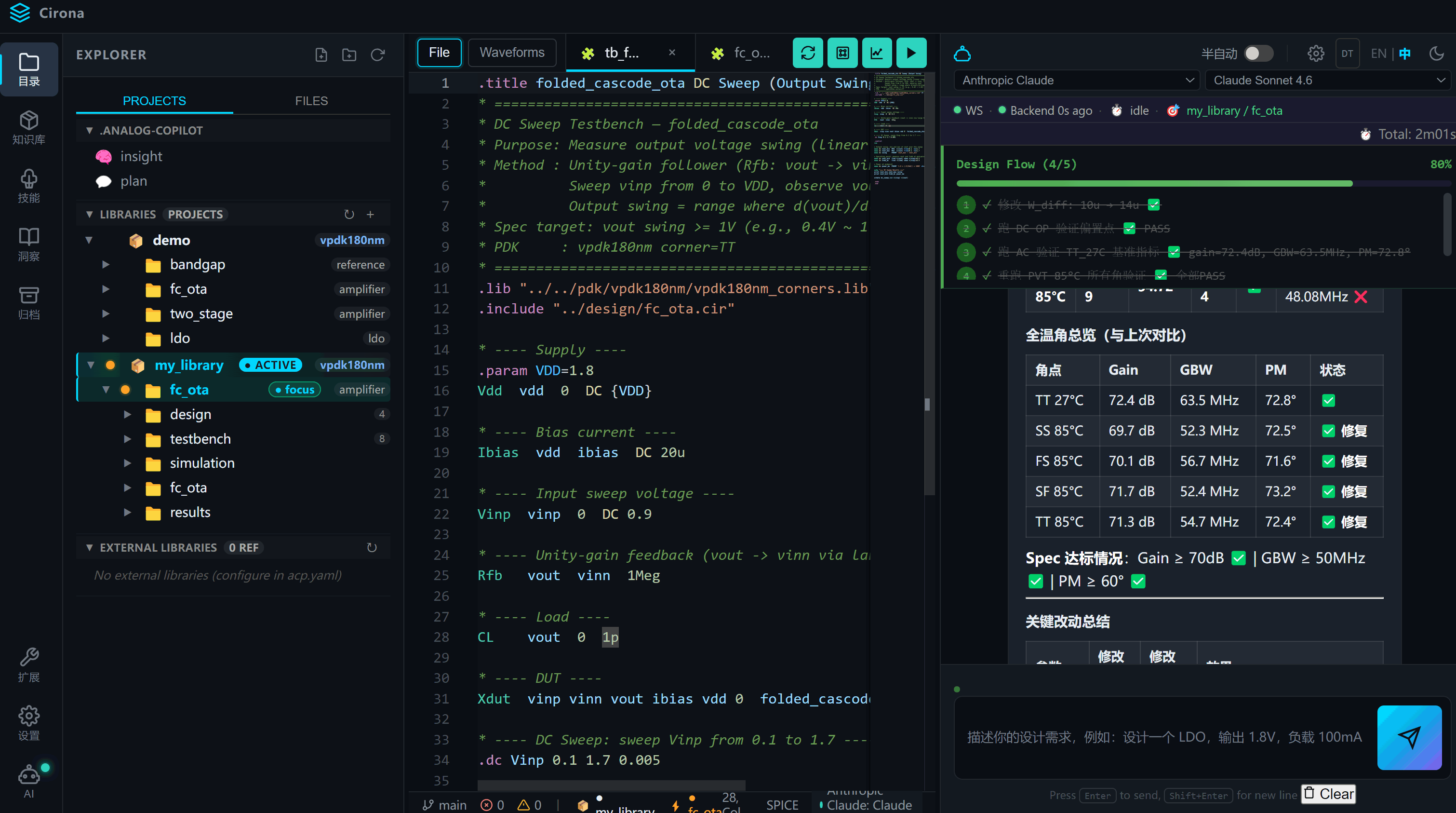

DC gain ≥ 70 dB, GBW 50 MHz, phase margin > 60°, 负载电容 = 1 pF, 功耗 < 500 µW; 工艺 vpdk180nm, Vdd = 1.8 V

Cirona 桌面版是装在个人电脑上的模拟电路设计 AI 工作环境,给每天消耗大量精力在 testbench、sizing 迭代、corner 验证等工作的工程师用。

龙虾火爆之后,同行们基于通用 agent 把 AI 接入芯片设计,在媒体上发表了很多文章;研究机构们也各自推出了芯片设计的专用 Agent。这些工作都很重要,为 AI 早日接入芯片设计做了很多探索和努力。但工程师们更关心的是何时能用上。

我们推出了不一样的:一个开箱即用的模拟电路设计 AI 原生开发平台 Cirona。

注:vpdk = virtual PDK。每代工艺关键参数(Vth / μCox / Vsat)在不同代工厂之间总是相似的,具体数值有差异。我们提供 vpdk 作为通用参考工艺;真实 PDK 因法律限制不能随产品分发。在 vpdk 上设计好的电路,mapping 到具体工艺时拓扑、sizing 思路、bias 策略都直接迁移,参数微调即可。

DC gain ≥ 70 dB, GBW 50 MHz, phase margin > 60°, 负载电容 = 1 pF, 功耗 < 500 µW; 工艺 vpdk180nm, Vdd = 1.8 V

Cirona 自动查找 Pack 知识库里的 OTA 设计流程,AI 根据 SPEC 选择拓扑结构,从 GBW 倒推 gm,从功耗倒推电流,按管子角色分配 headroom,等等,查表得到 W/L。

每一步公式和思考过程都有理有据。用户根据过程交互,可随时打断和调整。

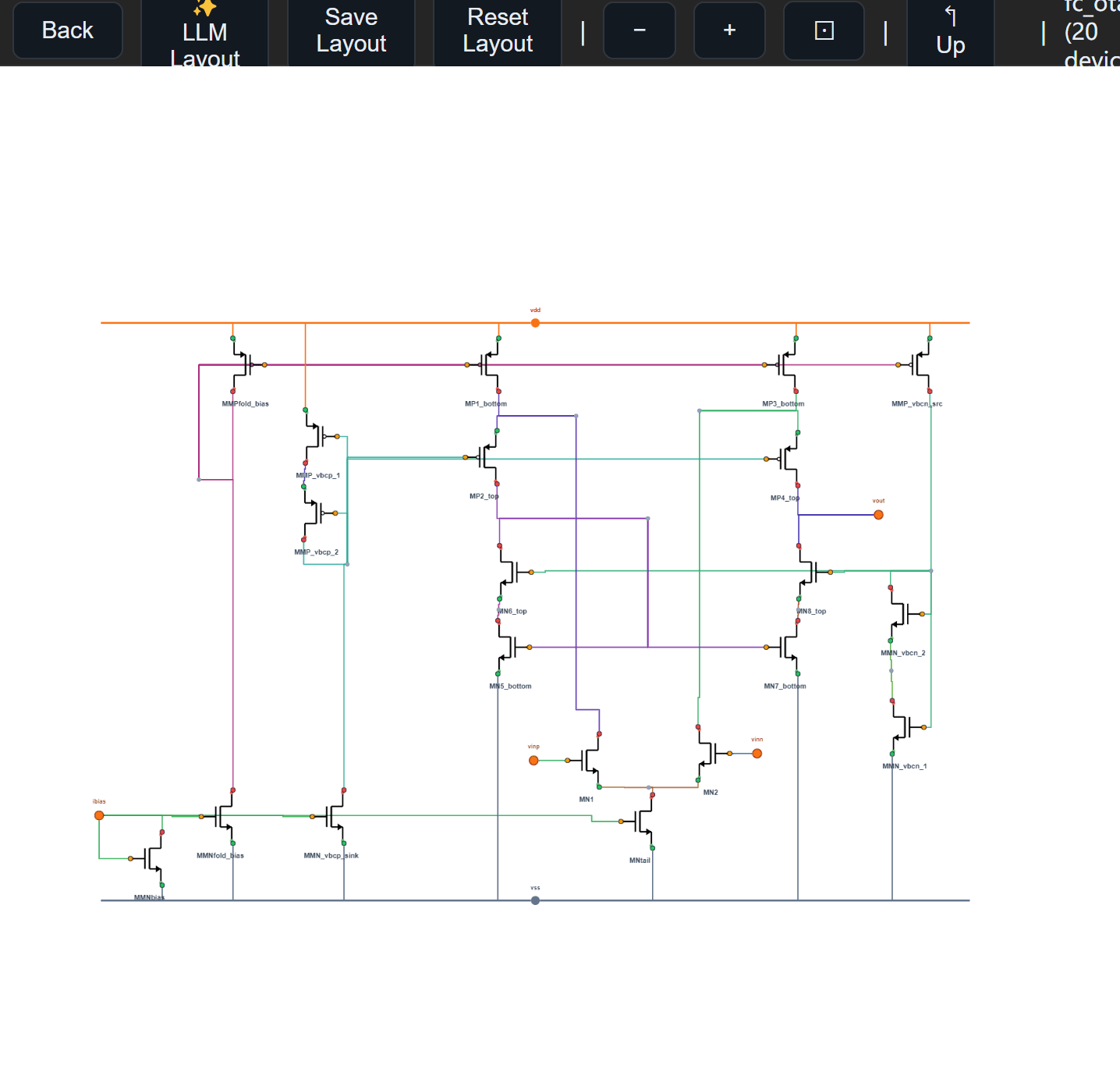

网表自动渲染成原理图,方便工程师审查电路设计。

跑完仿真,每颗管子的 gm、ID、Vds、Vov 列在表格里,饱和与否一眼看到。Bode 图、瞬态波形、节点电压在该出现的地方自然出现。

现在一句话:

起一个 80 trial 的优化任务,GBW 最大化,DC gain ≥ 70 dB,PM > 60°,并发 4 路。

内置贝叶斯 / CMA-ES / NSGA-II 多目标优化等优化算法,你看到的是「增益 vs 功耗 vs 带宽」的真实可达边界,而不是单点解。

这次的网表、bias 策略、踩过的坑就被打包成一个 Pack。下次遇到同样拓扑,装上你的 Pack,AI 无缝达成设计。

全程 Cirona 跑 80% 的执行:推导 sizing、写 testbench、参数调优、数据整理。但关键决策由工程师拍板:架构方向、spec 取舍、仿真内容。所有中间产物以工程师能审的形式呈现:原理图、表格、Bode 图等。

Cirona 是助手,帮你解决繁琐的活;核心还是工程师的思想。

你公司里最厉害的那位模拟老法师,三十年经验,脑子里装着无数模拟电路设计的经验和陷阱,如换了工艺后原来的架构就不能用了、LDO 零极点随输出电流变化导致的不稳定、Bandgap 启动电路设计不当而引起的良率问题,SDM-ADC 电容阵列 mismatch 的处理方法等。

从来没人写下来过。他退休那天,这些东西就跟着他一起走了。

我们的 Packs,可以把工程师的经验,永远留存下来。

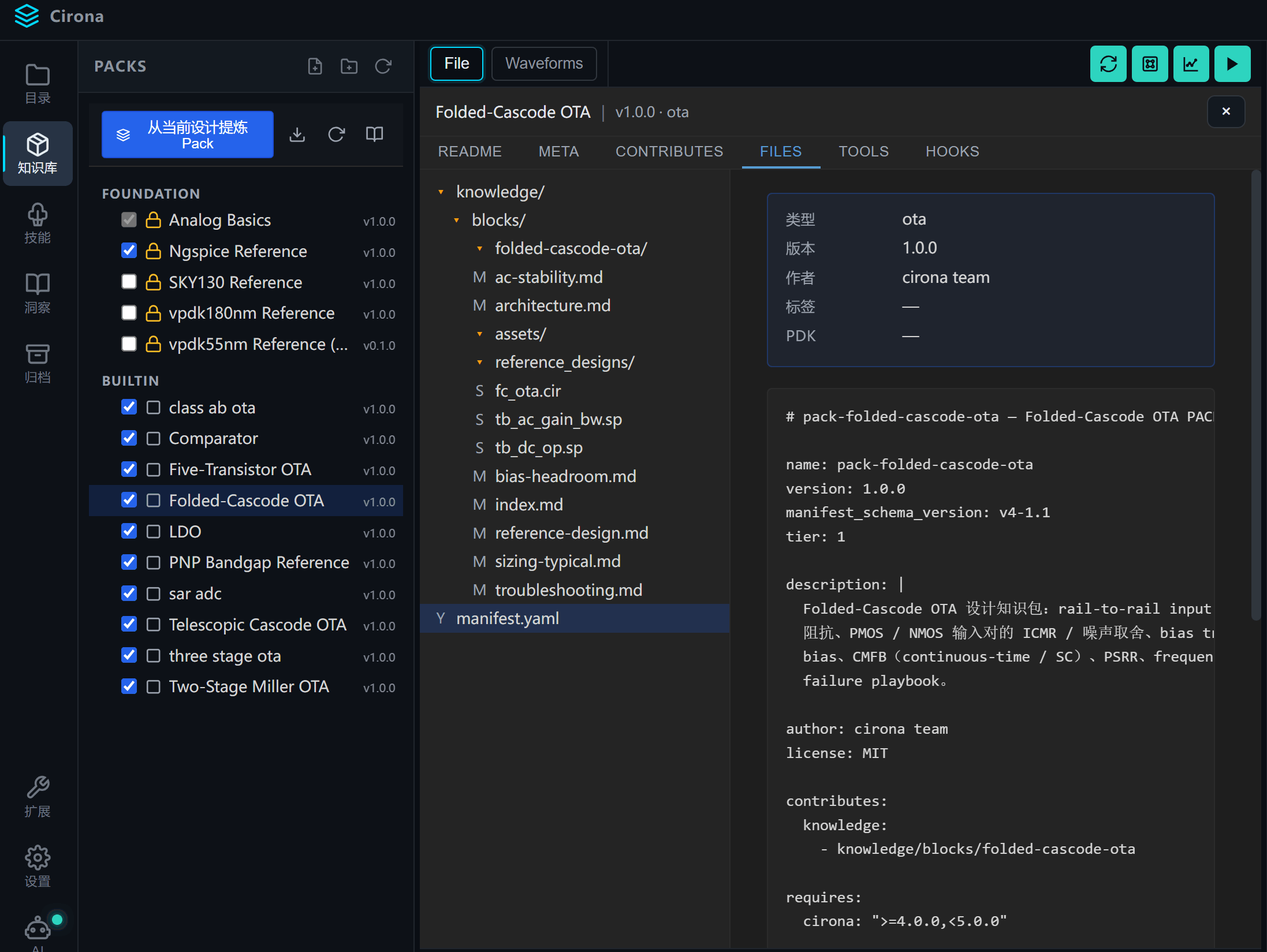

Packs 是什么?Packs 是 knowledge package 的简称,是电路知识、设计流程和经验的集合。

Pack 按目录结构组织。比如 folded-cascode_ota Pack 里放着 overview.md(拓扑是什么)/ design_flow.md(设计流程)/ reference_designs/(参考网表)/ failure_playbook.md(失败案例 + 诊断)/ lessons.yaml(历史经验)/ skills/(这个 Pack 专属的 skills)。

Skills 是现在 AI 圈里很火的概念。Skill 是描述某类做事步骤的提示模板,通用、跟行业解耦、跟工艺无关。这套范式做通用 agent 没问题,套到模拟 IC 上不行。

当前版本包括 Analog Design Flow、Device Sizing、Netlist Review、SDAS(Spec-Driven Architecture Screening)等,位于界面面板左边的技能插件栏。用户也可以定制自己的 Skill。

最简单的方法:完成一份设计之后,通过对话窗口输入「请帮我把这个设计方法和流程打包成一个 Pack」。Cirona 会引导完成 Pack 生成到本地工作目录。

一个工程师做出一个新拓扑的 Pack,那么装了这个 Pack 的 Agent 立刻多了一份能力。一千个工程师都贡献一份 Pack,那么 Agent 就可以获得一千份能力。

这是我们最看重的事。Pack 仓库托管在 GitHub,GPL-3.0 完全开源,鼓励衍生 Pack 持续回馈社区。我们希望它发展成一个开源社区 — 大家一起贡献 Pack,让 AI 辅助模拟电路设计的能力越来越强。

我们已经写了第一批 Pack(OTA 家族 / LDO / Bandgap / 比较器)。下一批 Pack 库扩展正在进行中,覆盖 ADC / PLL / 更多 OTA 的种类(class-AB、三级运放等)。也期望获得大家的支持和贡献。

接入 Linux 环境 + HSpice / Spectre 仿真器 + Virtuoso 联动。

开发中企业本地部署大模型,根据企业需求灵活定制。

规划中本地运行。内置 SPICE 仿真器,默认随产品分发主流开源 PDK。

v1.0.0-rc9.18 · 2026

Linux-1.0

(待更新)

让 AI 在模拟集成电路这个垂类,从「看起来能做」走到「反复地、可靠地做对」。